喜洋洋婚慶禮儀 締造完美婚禮的貼心伴侶

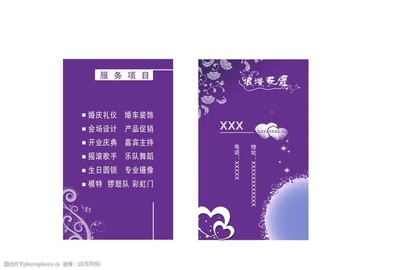

在人生最重要的時刻,一場浪漫而難忘的婚禮是每對新人夢寐以求的。喜洋洋婚慶禮儀,作為您身邊值得信賴的婚慶禮儀服務(wù)專家,致力于將這份夢想化為現(xiàn)實(shí)。我們擁有豐富的行業(yè)經(jīng)驗(yàn)和創(chuàng)意策劃團(tuán)隊(duì),秉承“細(xì)致、專業(yè)、創(chuàng)新”的服務(wù)理念,為每一對新人量身定制專屬婚禮方案。從場地布置、婚禮流程設(shè)計(jì)到主持人邀請、影像記錄,我們提供全程一站式服務(wù),確保每一個細(xì)節(jié)都盡善盡美。無論是典雅的中式婚禮照以喜慶莊重,還是西式儀式的溫馨愜意,喜洋洋婚慶都能助您在愛與承諾的誓言中閃耀全場。讓我們一起策劃您的良辰吉日,見證您的幸福笑容無需此行。加入我們,讓浪漫不分遲早,只因真愛感動時時刻刻溫暖人間!

如若轉(zhuǎn)載,請注明出處:http://www.jinqingmy.cn/product/36.html

更新時間:2026-05-15 05:39:01