集成電路CAD設計中的關鍵環節 芯片焊盤與版圖布局

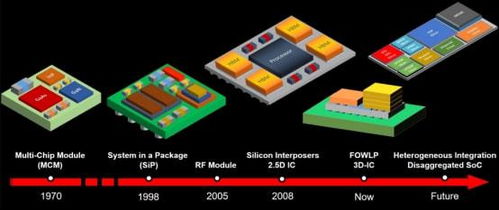

集成電路(IC)設計是一個高度復雜且精密的系統工程,其成功與否在很大程度上依賴于計算機輔助設計(CAD)工具的運用以及關鍵物理設計環節的把控。其中,芯片焊盤(Pad)設計與版圖(Layout)布局設計是連接電路邏輯與物理實現的核心橋梁,直接決定了芯片的性能、可靠性及可制造性。

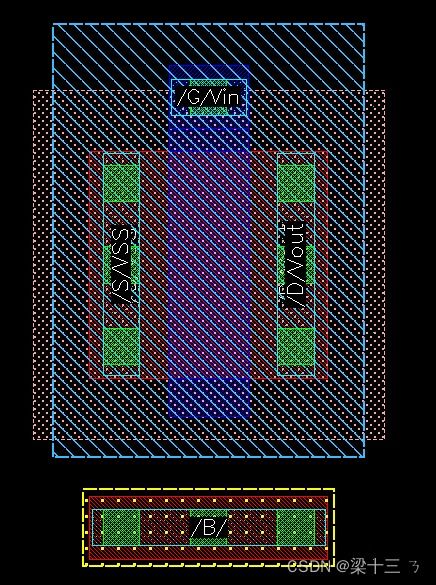

一、 芯片焊盤設計:芯片與外部世界的接口

芯片焊盤是集成電路芯片上用于與外部封裝引腳或電路板進行電氣連接和物理固定的金屬區域。其設計絕非簡單的金屬塊擺放,而需綜合考慮多方面的因素:

- 電氣特性:焊盤的尺寸、形狀及其與內部電路的連接線(通常為上金屬層)需要滿足電流承載能力(電流密度)、阻抗匹配以及信號完整性的要求。例如,電源和地焊盤通常需要更大的面積以減小電阻和電感,而高頻信號焊盤則需特別注意寄生參數的控制。

- 物理與可靠性:焊盤必須能夠承受封裝過程中的鍵合(Wire Bonding)或倒裝焊(Flip-Chip)所帶來的機械應力與熱應力。設計時需要遵循設計規則(Design Rule),確保與相鄰結構的間距,防止短路或長期可靠性問題(如電遷移)。

- 封裝兼容性:焊盤的布局(排列順序、間距)必須與選定的封裝形式(如QFP、BGA、CSP等)的引腳框架或基板相匹配。合理的焊盤布局能簡化封裝布線,提升良率。

- 測試與調試:通常會設置專用的測試焊盤,用于生產過程中的芯片探針測試(CP Test),以驗證晶圓級別的功能與性能。

在CAD設計流程中,焊盤通常作為一個特殊的庫單元(Pad Cell)進行設計和調用,其設計需要與封裝工程師密切協同。

二、 版圖布局設計:電路功能的物理映射

版圖布局是將經過邏輯綜合和電路設計(原理圖)驗證后的電路,轉化為一系列符合半導體制造工藝規則的幾何圖形(各層掩膜版圖形)的過程。這是IC設計從“抽象”走向“實體”的關鍵一步。

版圖設計的主要目標與挑戰包括:

- 面積優化:在滿足所有設計規則的前提下,盡可能減小芯片面積以降低制造成本。這需要對晶體管、標準單元、宏模塊(如存儲器、IP核)進行最緊湊的擺放(Floorplanning)。

- 性能優化:布局布線直接影響信號的延遲、功耗和噪聲。通過合理的布局,可以縮短關鍵路徑(Critical Path)的連線長度,減少寄生電阻和電容,從而提升芯片速度。電源網絡(Power Grid)的設計也至關重要,需確保整個芯片供電均勻穩定,壓降(IR Drop)在允許范圍內。

- 信號完整性:隨著工藝節點進步,互連線間的串擾(Crosstalk)、時鐘偏差(Skew)、電源地噪聲等問題愈發突出。版圖設計需要采用屏蔽、間距控制、插入緩沖器等手段來保障信號質量。

- 可制造性設計(DFM):現代版圖設計必須考慮光刻工藝的局限性,主動采用添加冗余圖形、進行光學鄰近效應修正(OPC)等DFM技術,以提高實際制造中的圖案保真度和良率。

- 可靠性設計(DFR):需考慮電遷移、熱載流子注入、閂鎖效應(Latch-up)等長期可靠性問題,并在版圖中通過增加接觸孔、添加保護環等結構進行預防。

三、 CAD工具在焊盤與版圖設計中的核心作用

整個設計流程高度依賴于專業的IC CAD(或稱EDA)工具鏈:

- 設計輸入與規劃:使用工具進行芯片的頂層規劃,確定焊盤環(Pad Ring)的位置、核心功能區域(Core Area)的劃分。

- 自動布局布線:對于數字電路,主要依靠自動布局布線工具,將數百萬甚至數十億個標準單元和宏模塊在設定的約束下進行擺放和連線。工具會根據時序、功耗、擁塞度等目標進行迭代優化。

- 物理驗證:這是確保設計成功的守門員。主要包括:

- 設計規則檢查:驗證版圖是否符合代工廠的工藝規則。

- 電路圖版圖一致性檢查:確保物理版圖與原始電路圖在電氣連接上完全一致。

- 寄生參數提取與后仿真:從完成的版圖中提取出詳細的寄生電阻、電容、電感參數,并反標回電路進行仿真,以精確驗證最終性能。

- 簽核:在交付制造前,進行包括時序、功耗、信號完整性、電源完整性在內的全面簽核分析,確保萬無一失。

結論

芯片焊盤設計與版圖布局設計是集成電路物理設計的兩個緊密相連的支柱。焊盤是芯片對外溝通的“港口”,其設計關乎封裝與測試的可行性;版圖則是內部電路運行的“城市藍圖”,其優劣直接決定了芯片的效能、成本與可靠性。在先進工藝節點下,這兩項工作的復雜性呈指數級增長,更加凸顯了先進CAD/EDA工具與深厚設計經驗相結合的重要性。成功的IC設計,必然是系統架構、電路設計、物理實現與制造工藝之間反復迭代、協同優化的結果,而焊盤與版圖正是這一過程中承上啟下的關鍵藝術與科學。

如若轉載,請注明出處:http://www.jinqingmy.cn/product/71.html

更新時間:2026-01-28 18:36:49