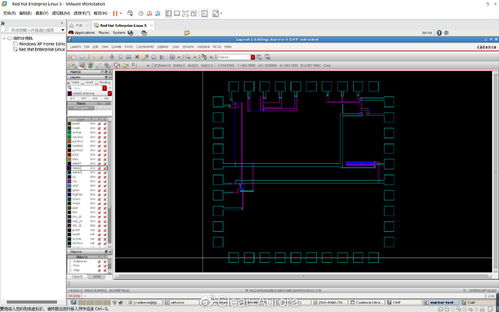

集成電路CAD設(shè)計(jì)中的關(guān)鍵環(huán)節(jié) 芯片焊盤與版圖布局設(shè)計(jì)探析

集成電路(IC)設(shè)計(jì)是一個(gè)高度復(fù)雜且精密的系統(tǒng)工程,而計(jì)算機(jī)輔助設(shè)計(jì)(CAD)工具的應(yīng)用極大地推動(dòng)了其發(fā)展。在IC設(shè)計(jì)的后端物理實(shí)現(xiàn)階段,芯片焊盤(Pad)設(shè)計(jì)與版圖(Layout)布局設(shè)計(jì)是兩個(gè)至關(guān)重要且緊密相連的環(huán)節(jié),直接決定了芯片的性能、可靠性、可制造性及最終成本。

一、 芯片焊盤設(shè)計(jì):芯片與外部世界的橋梁

芯片焊盤是集成電路裸片(Die)上用于與外部封裝引腳或基板進(jìn)行電氣連接和機(jī)械固定的金屬化區(qū)域。其設(shè)計(jì)絕非簡單的幾何圖形繪制,而需綜合考量電學(xué)、熱學(xué)、機(jī)械及工藝等多方面因素。

核心設(shè)計(jì)要點(diǎn)包括:

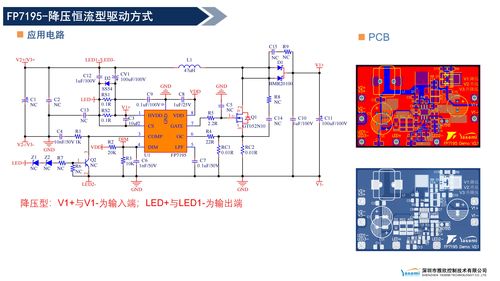

1. 電氣特性: 焊盤的大小、形狀及其與內(nèi)部電路的連接線(通常通過頂層金屬實(shí)現(xiàn))會(huì)影響信號(hào)完整性,尤其是高頻信號(hào)。需要考慮阻抗匹配、減小寄生電感與電容,以及防止信號(hào)串?dāng)_。對(duì)于電源和地焊盤,往往需要設(shè)計(jì)得更大或使用多個(gè)焊盤并聯(lián),以降低電阻和電感,確保穩(wěn)定的供電。

2. 可靠性: 焊盤需要承受封裝過程中的鍵合(如金絲球焊、楔形焊)或倒裝焊(Flip-Chip)帶來的機(jī)械應(yīng)力和熱應(yīng)力。設(shè)計(jì)需滿足一定的尺寸規(guī)則,確保鍵合強(qiáng)度,并考慮壓點(diǎn)區(qū)域(Bonding Area)與芯片內(nèi)部有源器件的安全距離(Keep-Out Area),防止應(yīng)力損傷。

3. 布局規(guī)劃: 焊盤通常沿芯片周邊排列(Perimeter Pad)或在芯片表面陣列分布(Area Array Pad,如Flip-Chip)。其位置規(guī)劃需與封裝類型(如QFP、BGA、CSP等)的引腳排布相匹配,同時(shí)優(yōu)化內(nèi)部走線,避免繞線過長。I/O焊盤環(huán)(I/O Pad Ring)的設(shè)計(jì)是芯片與核心邏輯區(qū)域的緩沖與接口。

4. ESD保護(hù): 每一個(gè)對(duì)外連接的焊盤都必須集成靜電放電(ESD)保護(hù)電路,以防止芯片在制造、測(cè)試、運(yùn)輸和使用過程中被靜電擊穿。ESD保護(hù)結(jié)構(gòu)的設(shè)計(jì)與焊盤布局需協(xié)同進(jìn)行。

二、 版圖布局設(shè)計(jì):性能與工藝的物理藍(lán)圖

版圖布局設(shè)計(jì)是將電路邏輯網(wǎng)表(Netlist)轉(zhuǎn)化為一系列符合制造工藝規(guī)則的幾何圖形(各層掩模圖形)的過程。它是電路設(shè)計(jì)思想的物理實(shí)現(xiàn),是性能、面積、功耗等指標(biāo)博弈的戰(zhàn)場(chǎng)。

核心設(shè)計(jì)原則與流程包括:

1. 規(guī)劃與分區(qū): 根據(jù)電路功能模塊(如模擬模塊、數(shù)字邏輯、存儲(chǔ)器、電源管理等)進(jìn)行芯片面積的初步規(guī)劃與分區(qū)。合理的布局可以縮短關(guān)鍵路徑連線,減少信號(hào)延遲和互連寄生效應(yīng),同時(shí)有利于電源網(wǎng)絡(luò)的均勻分布。

2. 單元布局與布線: 使用CAD工具進(jìn)行標(biāo)準(zhǔn)單元或定制單元的自動(dòng)布局(Placement)和布線(Routing)。布局追求連線總長最短、時(shí)序收斂;布線則需在有限的互連層資源中完成所有邏輯連接,并滿足設(shè)計(jì)規(guī)則檢查(DRC)和電氣規(guī)則檢查(ERC)。

3. 時(shí)鐘樹綜合: 為整個(gè)芯片構(gòu)建低偏移(Skew)、低延遲的時(shí)鐘分布網(wǎng)絡(luò),是高性能數(shù)字芯片布局中的核心任務(wù)。時(shí)鐘樹的拓?fù)浣Y(jié)構(gòu)和物理布局直接影響芯片的最高工作頻率。

4. 電源/地網(wǎng)絡(luò)設(shè)計(jì): 設(shè)計(jì) robust 的電源(VDD)和地(VSS)網(wǎng)格,為所有電路模塊提供穩(wěn)定、低噪聲的供電。這涉及電源環(huán)(Power Ring)、電源條帶(Power Stripe)以及大量通孔(Via)的設(shè)計(jì),需考慮電流密度和電壓降(IR Drop)。

5. 設(shè)計(jì)驗(yàn)證: 布局完成后,必須進(jìn)行一系列嚴(yán)格的驗(yàn)證,包括DRC(確保圖形符合工藝制造極限)、LVS(版圖與電路圖一致性檢查)、寄生參數(shù)提取(RC Extraction)以及基于帶寄生參數(shù)的時(shí)序分析(Post-Layout Simulation)和信號(hào)完整性分析(如串?dāng)_、電遷移)。

三、 焊盤設(shè)計(jì)與版圖布局的協(xié)同

焊盤設(shè)計(jì)與整體版圖布局并非孤立進(jìn)行,而是需要深度協(xié)同:

- 接口與規(guī)劃: I/O焊盤環(huán)的布局是芯片版圖規(guī)劃的第一步,它框定了核心區(qū)域(Core Area)的范圍。焊盤的位置決定了I/O信號(hào)進(jìn)入芯片的入口點(diǎn),進(jìn)而影響內(nèi)部模塊的布局和全局布線的走向。

- 電源完整性: 電源和地焊盤的數(shù)量、位置以及它們與內(nèi)部電源網(wǎng)格的連接方式,共同決定了電源配送網(wǎng)絡(luò)的阻抗和噪聲水平。

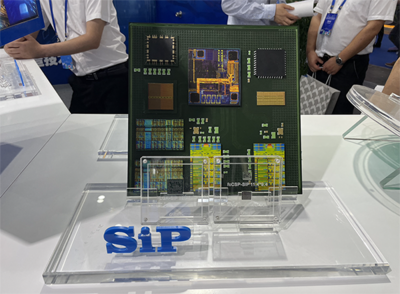

- 封裝協(xié)同設(shè)計(jì): 現(xiàn)代高性能芯片往往需要與封裝進(jìn)行協(xié)同設(shè)計(jì)(Co-Design)。焊盤的布局(尤其是Flip-Chip的凸點(diǎn)布局)必須與封裝基板的布線能力、熱膨脹系數(shù)匹配以及散熱路徑規(guī)劃相結(jié)合。

###

集成電路CAD設(shè)計(jì)中的芯片焊盤與版圖布局設(shè)計(jì),是將抽象電路轉(zhuǎn)化為可制造硅片的關(guān)鍵橋梁。它們深度融合了電路知識(shí)、物理理解、工藝技術(shù)和工程經(jīng)驗(yàn)。隨著工藝節(jié)點(diǎn)不斷演進(jìn)至納米尺度,以及系統(tǒng)級(jí)封裝(SiP)、芯粒(Chiplet)等新技術(shù)的興起,這兩項(xiàng)設(shè)計(jì)工作面臨的挑戰(zhàn)日益嚴(yán)峻,其重要性也愈加凸顯。優(yōu)秀的焊盤與版圖設(shè)計(jì),是保證芯片一次流片成功、達(dá)成預(yù)期性能指標(biāo)的堅(jiān)實(shí)基石。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://www.jinqingmy.cn/product/49.html

更新時(shí)間:2026-01-06 22:44:01